Update: Intel Accelerated Ireland EUV Fab Ramp-Up as Meteor Lake Chips Were In Short Supply

by Ryan Smith on August 1, 2024 8:15 PM EST- Posted in

- CPUs

- Intel

- Meteor Lake

- Intel 4

Update 08/02: Patrick Moorhead has published a further tweet, clarifying that "Pat [Gelsinger] didn’t tell me l that there were yield issues. This was *my* interpretation." The text of the article has been updated accordingly to reflect this tweet, as well as Intel statements about accelerating their Ireland Fab 34 ramp-up.

Alongside Intel’s weak Q2 2024 earnings report and the announcement of $10 billion in spending cuts and layoffs for 2025, the company is also disclosing some new information about their chip deliveries over the first half of the year. A brief report, posted on X by analyst Patrick Moorhead and citing a conversation with Intel CEO Pat Gelsinger, revealed that Intel encountered a major production bottleneck on Meteor Lake earlier this year. The issue was significant enough to drive intel to take the extraordinary and costly step of accelerating their Ireland fab ramp-up in order to improve chip capacity.

It was a very rough Q2 for $INTC. And that guide... Thanks, @Pgelsinger, for the time to discuss.

— Patrick Moorhead (@PatrickMoorhead) August 1, 2024

It appears that there were yield/throughput issues on Meteor Lake, negatively impacting gross margins. When you have to get the product to your customers, and you have wafers to… pic.twitter.com/pHU66xvFe7

-Patrick Moorhead

In a separate tweet posted several hours later, Moorhead then clarified that the yield issues mentioned in his first tweet were his interpretation of the matter, rather than something Pat Gelsinger had told him directly.

-Patrick Moorhead

Decoding Moorhead’s dense tweets, fundamentally, Moorhead is questioning why Intel's Cost of Goods Sold (COGS) – how much the company's chips cost to produce – were on the rise with the launch of Meteor Lake. The analyst surmised that yields and/or some other unexpected production bottleneck must be the case, as these are the typical issues that drive up chip COGS on a short-term basis like Intel has been experiencing.

And, judging from Intel's earnings call that took place after the initial tweet, Moorhead was right to an extent. Referencing the increased COGS, Intel CFO David Zinsner noted that Intel opted to ramp up its high-volume production in Ireland faster than initially planned. This increased Intel's capacity for Intel 4 (and Intel 3) capacity, but doing so also increased their costs, as wafers out of Ireland cost more in the near term.

-Intel CFO David Zinsner (Intel Q2'24 Earnings Call)

Between Moorhead's report that OEMs have been receiving fewer Meteor Lake chips than they could use, and Intel's announcement that they accelerated the Ireland fab ramp-up, this is the first significant disclosure that Meteor Lake chips were, at least at some point, in unexpectedly short supply. Which in turn required Intel to take unexpected and extraordinary steps in order to improve chip production, at the cost of lower short-term profit margins and higher COGS.

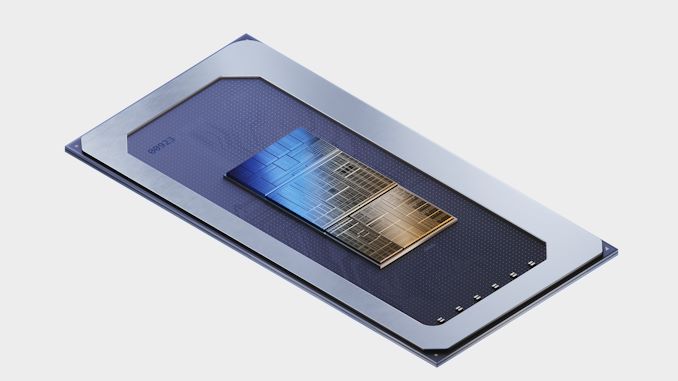

The first of Intel's high-volume manufacturing (HVM) fabs to be equipped for the Intel 4 and Intel 3 processes, Fab 34 in Ireland is a critical element to Intel's cutting-edge product plans over the next couple years. Intel was not initially planning on relying so much on Fab 34 this soon – instead using their Oregon development fabs to do more of their Intel 4 & Intel 3 fabrication – but the company opted to ramp up at a faster pace. The benefit to Intel is that they get more fab capacity sooner, but it means they're incurring around $1 billion in costs now of what would have otherwise been spread out over further quarters during a more gradual ramp-up.

The net result was that, while Intel took a margin hit, it also allowed them to supply more Meteor Lake chips than they otherwise would have, even beating their own previous projections for Q2 shipments. Overall, Intel reported in their Q2 earnings that they’ve shipped 15 million “AI PC” chips since Meteor Lake’s launch, though the company doesn't break down how many of those were in Q2 versus Q1 and Q4'23. Still, according to Moorhead, this was fewer chips than OEMs would have liked to have, and they would have taken more chips if they were available.

COGS and Ireland ramp-ups aside, Moorhead also posits that some of Intel's capacity boost came from running “hot lots” of Meteor Lake – high priority wafer batches that get moved to the front of the line in order to be processed as soon as possible (or as reasonably close as is practical). Hot lots are typically used to get highly-demanded chips produced quickly, getting them through a fab sooner than the normal process would take. As a business tool, hot lots are a fact of life of chip production, but they’re undesirable because in most cases they cause disruptions to other wafers that are waiting their turn to be processed.

If true, running hot lots of Meteor Lake would be a significant development given the potential disruptions. At the same time, however, the situation with Meteor Lake is somewhat particular, as the Intel 4 process used for Meteor Lake’s compute tile (the only active tile made at Intel) is not offered to external foundry customers, or even used by other Intel CPUs (Xeon 6s all use Intel 3). So hot lots of Meteor Lake would have few other wafers to even jump ahead of for EUV tooling (Intel would certainly not put them ahead of high-margin Xeon products), while it's unclear how this would cascade down to any tools shared with Intel 7.

Intel, for their part, did not comment on Meteor Lake chip yields or hot lots in their earnings call.

In any case, Intel at this point is looking to turn around their troubled fortunes in the second half of this year. The company’s next-gen client SoC for mobile, Lunar Lake, is set to launch on September 3rd. And notably, both of its active tiles are being built by TSMC. So Lunar Lake would be spared from any Intel logic fab bottlenecks, though it still has to go through Intel’s facilities for assembly using their Foveros technology. And there remains the thorny issue of higher production costs altogether, since Intel is paying for what's effectively the fully outsourced production of a Core CPU.

28 Comments

View All Comments

heffeque - Thursday, August 1, 2024 - link

Things are looking mighty "high temperature" for Intel... and not in a good way.ballsystemlord - Thursday, August 1, 2024 - link

What exactly does "bone dry" mean in this context?I'm an English native and I've never have known what the heck this guy was saying if it wasn't for a translation.

GeoffreyA - Friday, August 2, 2024 - link

He is not lucid. I suppose it means the wafers were not ready? Perhaps a "dry wafer" is chip-manufacturing idiom for finished, ready to be cut? We know lots of water is used, so conceivably, wafers are wet at some point?Ryan Smith - Friday, August 2, 2024 - link

"Bone dry" in this context would mean that OEMs would not be receiving any MTL chips.The analogy is a water well; if there isn't any water available, it's said to be bone dry.

In this case, the flow of MTL chips was *not* bone dry; hence OEMs got chips. Just not enough of them.

ballsystemlord - Friday, August 2, 2024 - link

Thanks!eastcoast_pete - Friday, August 2, 2024 - link

In industrial gases, bone dry grade means no detectable moisture. So, very dry indeed.ballsystemlord - Friday, August 2, 2024 - link

Thanks for the cross industry interpretation. I found it fascinating.ikjadoon - Thursday, August 1, 2024 - link

That’s very interesting. Intel 4 MTL used a tiny little die and still they had a very high defect rate?Intel never mentioned these issues for the past six months. Why are they coming out all of a sudden?

That is…demonically bad. You only made one tile, Intel. You’ve launched nodes before.

Abundantly clear MTL was so overhyped. Didn’t get a desktop release. Didn’t even satisfy the full notebook market. Battery life was meh. The bottleneck was Intel’s flagship node. Shifted to overseas in Ireland last-minute from Oregon.

And Pat Geisinger wants to fab Apple’s CPUs. I don’t know how anyone still believes this guy.

sharath.naik - Friday, August 2, 2024 - link

That's because intel 4 is really 7NM using their EUV (not deep EUV), 7nm is at the edge of what you can do with EUV. being at the edge means high defect rates. This is not something Intel can really fix. The best they can do is go slow reduce the defect rates. But I guess they took a decision that they can get more end result with high rejections being fast than low rejection being slow.They are stuck in this until they get those machines for d-EUV. and those will only trickle in over the period of year or more.

Bulat Ziganshin - Wednesday, August 7, 2024 - link

DUV means deep ultra-violet (used by Intel and other Western manufacturers up to 12 nm), EUV means Extreme ultraviolet (used for 10 nm and smaller). There is no "deep EUV"