TSMC: Performance and Yields of 2nm on Track, Mass Production To Start In 2025

by Anton Shilov on May 30, 2024 3:00 PM EST- Posted in

- Semiconductors

- TSMC

- 2nm

- N2

- N2P

- TSMC Symposium 2024

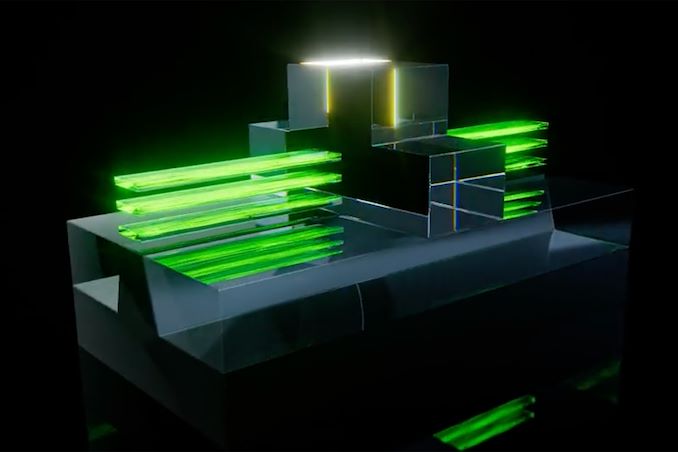

In addition to revealing its roadmap and plans concerning its current leading-edge process technologies, TSMC also shared progress of its N2 node as part of its Symposiums 2024. The company's first 2nm-class fabrication node, and predominantly featuring gate-all-around transistors, according to TSMC N2 has almost achieved its target performance and yield goals, which places it on track to enter high-volume manufacturing in the second half of 2025.

TSMC states that 'N2 development is well on track and N2P is next.' In particular, gate-all-around nanosheet devices currently achieve over 90% of their expected performance, whereas yields of 256 Mb SRAM (32 MB) devices already exceeds 80%, depending on the batch. All of this for a node that is over a year away from mass production.

Meanwhile, average yield of a 256 Mb SRAM was around 70% as of March, 2024, up from around 35% in April, 2023. Device performance has also been improving with higher frequencies being achieved while keeping power consumption in check.

Chip designer interest towards TSMC's first 2nm-class gate-all-around nanosheet transistor-based technology is significant, too. The number of new tape-outs (NTOs) in the first year of N2 is over two-times higher than it was for N5. Though with that said, given TSMC's close working relationship with a handful of high-volume vendors – most notably Appe – NTOs can be a very misleading figure since the first year of a new node at TSMC is capacity constrained, and consequently the bulk of that capacity goes to TSMC's priority partners.

Meanwhile, there were considerably more N5 tapeouts in its second year (some where N5P, of course) and N2 promises to have 2.6X more NTOs in its second year. So the node indeed looks quite promising. In fact, based on TSMC's slides (which we're unfortunately not able to republish), N2 is more popular than N3 in terms of NTOs both in the first and the second years of existence.

When it comes to the second year of N2, in the second half of 2026 TSMC plans to roll out its N2P technology, which promises additional performance and power benefits. N2P is expected to improve frequency by 15% - 20%, reduce power consumption by 30% - 40%, and increase chip density by over 1.15 times compared to N3E, significant benefits to move to all-new GAA nanosheet transistors.

Finally, for those companies that need the best in performance, power, and density, TSMC is poised to offer their A16 process in 2026. That node will also bring in backside power delivery, which will add costs, but is expected to greatly improve performance efficiency and scaling.

Source: TSMC Symposium 2024

9 Comments

View All Comments

SanX - Thursday, May 30, 2024 - link

Good for mobiles, something for desktop and nothing server chips. Looks like these fake nanometers started to fly like hot cakes with increased frequency. Actual density does not change at all. If transistor size was 43x43 nm with 5-7nm it still will be may be 40x40 nm with 2 nm.Before switch to each new step in nm technology meant geometrical doubling density and more cores. Now it means nothing, just couple tens percents in power efficiency.

If currently with 5-7nm you get 100-core server chips, in good old days at 2nm you would get almost (7nm/2nm)^2=1225 cores but with that nm race you will only get announcement of another great nm "breakthrough".

Zoolook13 - Friday, May 31, 2024 - link

It was a very long time since a new node was a true halving in size in both x and y and you could evn say there never was, besides that was in the good old days of planar transistors.With FinFet we moved into 3D transistors and now we move into vertical stacking so even if the old planar measurements seem to indicate stagnation it isn't as bad as you try to make it out to be.

nandnandnand - Saturday, June 1, 2024 - link

"Good for mobiles, something for desktop and nothing server chips."I guess power efficiency doesn't matter for servers? I'll tell them to spin up some new nuclear power plants.

SanX - Sunday, June 2, 2024 - link

When flying over USA have you noticed the land divided by squares ? These are typically 1 square mile private lands mostly for agriculture. Just one such square covered by solar panels (with modern batteries for night use) is enough to feed first 3 largest TOP500 supercomputers -- Frontier, Aurora and Microsoft one.Surfacround - Tuesday, June 4, 2024 - link

to quote the internet “ A 1 MW turbine produces on average about 0.3 MW. A 1 MW solar farm produces on average about 0.15 MW. So you would need a 2 MW solar farm to produce the same power as 1 MW wind turbine. Assuming the PV panels are 0.435 kW which is a common size, you would need about 4600 panels.”so might be better off with wind turbines… (and not being off-topic, lol)

Threska - Sunday, June 2, 2024 - link

Bioprocessors are the future.https://tinyurl.com/zexw249w

Blastdoor - Friday, May 31, 2024 - link

I've read speculation that apple will use N2 in 2025, but I'm skeptical that can really happen if high volume manufacturing doesn't until the 2nd half. Allegedly HVM of N3 began in December 2022 and Apple didn't release an N3 based product until September of 2023 -- nine months later. So even if "second half of 2025" means July 1st, we shouldn't expect Apple to ship these chips in a product until first quarter of 2026.my_wing - Sunday, June 2, 2024 - link

"Finally, for those companies that need the best in performance, power, and density, TSMC is poised to offer their A16 process in 2026. That node will also bring in backside power delivery, which will add costs, but is expected to greatly improve performance efficiency and scaling."Intel mentioned that BSPD is going to "Reduce" cost not "Increase" i.e. reduce in total number of layer.

TSMC is so Doomed

my_wing - Monday, June 3, 2024 - link

Some comments in other TSMC articles never delay.Yes they don't because they nowdays nodes is just marketing names

So if N3B fails and delay so what I just rename N5+++ to N3E wow I have a working N3 (wow 3nm) oh so great.

So if N2P is fail and delay so what I just rename N2 and then push a new name A16, now I am on schedule, oh yes TSMC always on schedule but the "rename" schedule

Which is ""Meaningless"""