Stratix 10

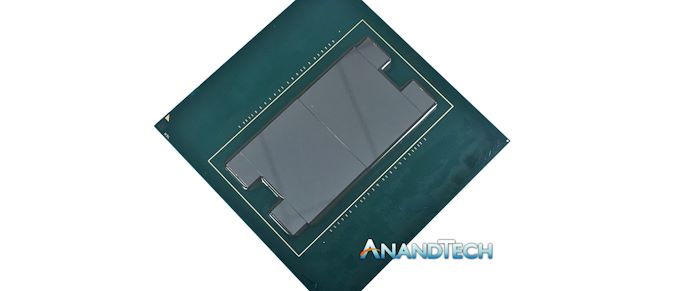

The best thing about manufacturing Field Programmable Gate Arrays (FPGAs) is that you can make the silicon very big. The nature of the repeatable unit design can absorb issues with a process technology, and as a result we often see FPGAs be the largest silicon dies that enter the market for a given manufacturing process. When you get to the limit of how big you can make a piece of silicon (known as the reticle limit), the only way to get bigger is to connect that silicon together. Today Intel is announcing its latest ‘large’ FPGA, and it comes with a pretty big milestone with its connectivity technology.

Intel Ships Stratix 10 DX FPGAs: Supports PCIe 4.0, UPI, and Optane DCPMM

Last week Intel announced it has started shipments of its Stratix 10 DX FPGA to early adopters. The DC models are designed for next-generation cache-coherent accelerators for custom servers...

4 by Anton Shilov & Dr. Ian Cutress on 10/3/2019Intel Launches Stratix 10 TX: Leveraging EMIB with 58G Transceivers

One of the key takeaways from Hot Chips last year was that Intel’s EMIB strategy was going to be fixed primarily in FPGAs to begin with. Intel instigated a...

7 by Ian Cutress on 2/26/2018