HPC

Arm this week introduced its Arm Total Design initiative, which is aimed at accelerating development of custom datacenter-oriented system-on-chip (SoC) designs using Neoverse Compute Subsystems (CSS). The collaborative ecosystem unites various developers in a bid to speed up time-to-market and reduce development costs of custom SoCs for AI, cloud, and high-performance computing markets. ATD promises to enable development of datacenter processors that will offer formidable competition for x86 CPUs. The Arm Total Design ecosystem is a conglomerate of ASIC design houses, IP vendors, EDA tool providers, foundries, and firmware developers that is aimed to facilitate rapid and cost-efficient delivery of custom silicon for datacenters based on Arm Neoverse cores for AI, HPC, cloud, and networking workloads. The ecosystem provides preferential access to Neoverse CSS to...

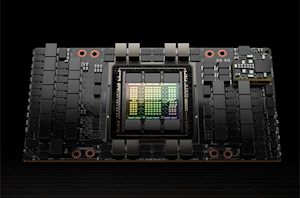

Cloud Provider Gets $2.3 Billion Debt Using NVIDIA's H100 as Collateral

CoreWeave, an NVIDIA-backed cloud service provider specializing in GPU-accelerated services, has secured a debt facility worth $2.3 billion using NVIDIA's H100-based hardware as collateral. The company intends to use...

18 by Anton Shilov on 8/4/2023The Aurora Supercomputer Is Installed: 2 ExaFLOPS, Tens of Thousands of CPUs and GPUs

Argonne National Laboratory and Intel said on Thursday that they had installed all 10,624 blades for the Aurora supercomputer, a machine announced back in 2015 with a particularly bumpy...

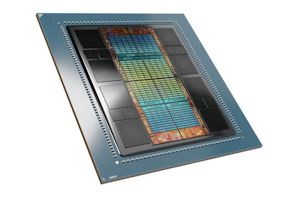

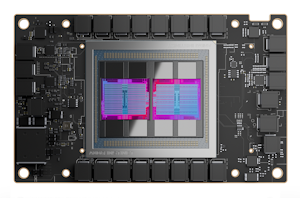

39 by Anton Shilov on 6/22/2023AMD Expands AI/HPC Product Lineup With Flagship GPU-only Instinct MI300X with 192GB Memory

Alongside their EPYC server CPU updates, as part of today’s AMD Data Center event, the company is also offering an update on the status of their nearly-finished AMD Instinct...

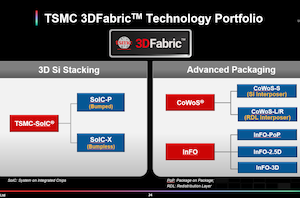

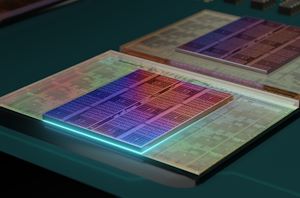

28 by Ryan Smith on 6/13/2023TSMC Preps 6x Reticle Size Super Carrier Interposer for Extreme SiP Processors

As part of their efforts to push the boundaries on the largest manufacturable chip sizes, Taiwan Semiconductor Manufacturing Co. is working on its new Chip-On-Wafer-On-Substrate-L (CoWoS-L) packaging technology that...

2 by Anton Shilov on 5/26/2023Intel HPC Updates For ISC 2023: Aurora Nearly Done, More Falcon Shores, and the Future of XPUs

With the annual ISC High Performance supercomputing conference kicking off this week, Intel is one of several vendors making announcements timed with the show. As the crown jewels of...

15 by Ryan Smith on 5/22/2023Supermicro Lists Intel Data Center GPU Max 'Ponte Vecchio' Based Machines

Supermicro this week began to list the industry's first commercial servers based on Intel's Data Center GPU Max 'Ponte Vecchio' compute GPUs. The machines use Ponte Vecchio in add-in-board...

1 by Anton Shilov on 5/4/2023Fujitsu Preps Monaka Datacenter CPU to Succeed A64FX: Greater Efficiency and More Features

Fujitsu has revealed that the company is prepping the successor for its A64FX processor for high-performance computing. The company's second-generation Arm-based server CPU is slated to offer considerably higher...

21 by Anton Shilov on 3/10/2023Intel Scraps Rialto Bridge GPU, Next Server GPU Will Be Falcon Shores In 2025

On Friday afternoon, Intel published a letter by Jeff McVeigh, the company’s interim GM of their Accelerated Computing Systems and Graphics group (AXG). In it, McVeigh offered a brief...

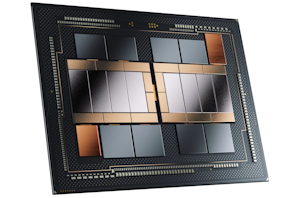

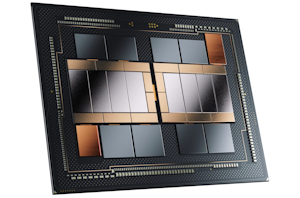

47 by Ryan Smith on 3/4/2023CES 2023: AMD Instinct MI300 Data Center APU Silicon In Hand - 146B Transistors, Shipping H2’23

Alongside AMD’s widely expected client product announcements this evening for desktop CPUs, mobile CPUs, and mobile GPUs, AMD’s CEO Dr. Lisa Su also had a surprise up her sleeve...

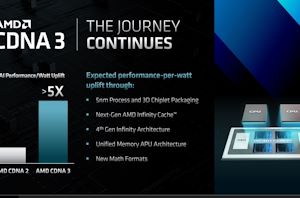

38 by Ryan Smith on 1/5/2023AMD: Combining CDNA 3 and Zen 4 for MI300 Data Center APU in 2023

Alongside their Zen CPU architecture and RDNA client GPU architecture updates, AMD this afternoon is also updating their roadmap for their CDNA server GPU architecture and related Instinct products...

16 by Ryan Smith on 6/9/2022Intel Unveils Rialto Bridge: Second-Gen Xe-HPC Accelerator to Succeed Ponte Vecchio

With ISC High Performance 2022 taking place this week in Hamburg, Germany, Intel is using the first in-person version of the event in 3 years to offer an update...

38 by Ryan Smith on 5/31/2022Intel Showcases Sapphire Rapids Plus HBM Xeon Performance at ISC 2022

Alongside today’s disclosure of the Rialto Bridge accelerator, Intel is also using this week’s ISC event to deliver a brief update on Sapphire Rapids, the company’s next-generation Xeon CPU...

22 by Ryan Smith on 5/31/2022AMD Releases Instinct MI210 Accelerator: CDNA 2 On a PCIe Card

With both GDC and GTC going on this week, this is a big time for GPUs of all sorts. And today, AMD wants to get in on the game...

39 by Ryan Smith on 3/22/2022AMD Releases Milan-X CPUs With 3D V-Cache: EPYC 7003 Up to 64 Cores and 768 MB L3 Cache

There's been a lot of focus on how both Intel and AMD are planning for the future in packaging their dies to increase overall performance and mitigate higher manufacturing...

58 by Gavin Bonshor on 3/21/2022Intel Goes Full XPU: Falcon Shores to Combine x86 and Xe For Supercomputers

One of Intel’s more interesting initiatives over the past few years has been XPU – the idea of using a variety of compute architectures in order to best meet...

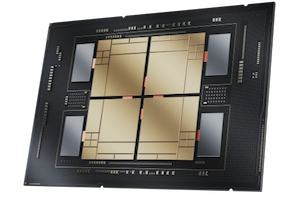

28 by Ryan Smith on 2/17/2022Intel: Sapphire Rapids With 64 GB of HBM2e, Ponte Vecchio with 408 MB L2 Cache

This week we have the annual Supercomputing event where all the major High Performance Computing players are putting their cards on the table when it comes to hardware, installations...

69 by Dr. Ian Cutress on 11/15/2021AMD Announces Instinct MI200 Accelerator Family: Taking Servers to Exascale and Beyond

AMD today is formally unveiling their AMD Instinct MI200 family of server accelerators. Based on AMD’s new CDNA 2 architecture, the MI200 family is the capstone AMD’s server GPU...

61 by Ryan Smith on 11/8/2021Intel's Aurora Supercomputer Now Expected to Exceed 2 ExaFLOPS Performance

As part of Intel’s 2021 Innovation event, the company offered a brief update on the Aurora supercomputer, which Intel is building for Argonne National Laboratory. The first of the...

14 by Ryan Smith on 10/27/2021Hot Chips 2021 Keynote Live Blog: Department of Energy on AI Chips

Welcome to Hot Chips! This is the annual conference all about the latest, greatest, and upcoming big silicon that gets us all excited. Stay tuned during Monday and Tuesday...

0 by Dr. Ian Cutress on 8/24/2021