Examining Intel's Ice Lake Processors: Taking a Bite of the Sunny Cove Microarchitecture

by Dr. Ian Cutress on July 30, 2019 9:30 AM EST- Posted in

- CPUs

- Intel

- 10nm

- Microarchitecture

- Ice Lake

- Project Athena

- Sunny Cove

- Gen11

Thunderbolt 3: Now on the CPU*

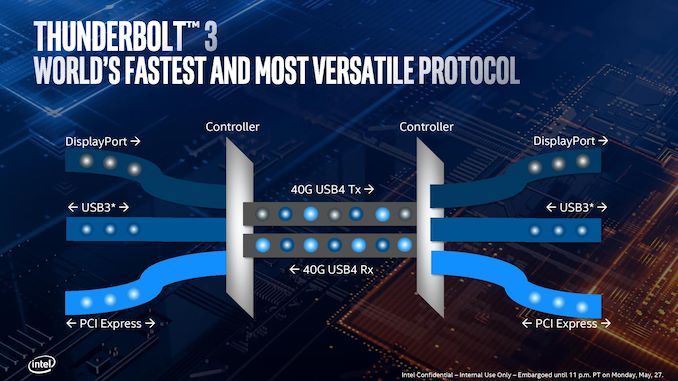

One of the big failures of the Thunderbolt technology since its inception has been its adoption beyond that Apple ecosystem. In order to use it, both the host and the device needed TB controllers supplied by Intel. It wasn’t until Thunderbolt 3 started to use USB Type-C, and Thunderbolt 3 having enough bandwidth to support external graphics solutions, that we started to see the number of available devices start to pick up. The issue still remains that the host and device need an expensive Intel-only controller, but the ecosystem was starting to become more receptive to its uses.

With Ice Lake, that gets another step easier.

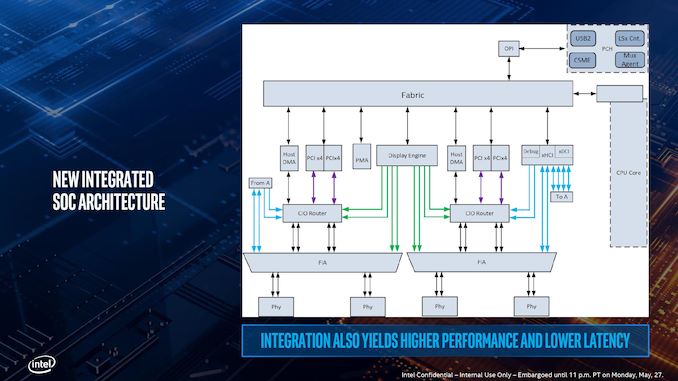

Rather than bundle TB3 support into the chipset, Intel has integrated it on the die of Ice Lake, and it takes up a sizable amount of space. Each Ice Lake CPU can support up to four TB3 ports, with each TB3 port getting a full PCIe 3.0 x4 root complex link internally for full bandwidth. (For those keeping count, it means Ice Lake technically has 32 PCIe 3.0 lanes total).

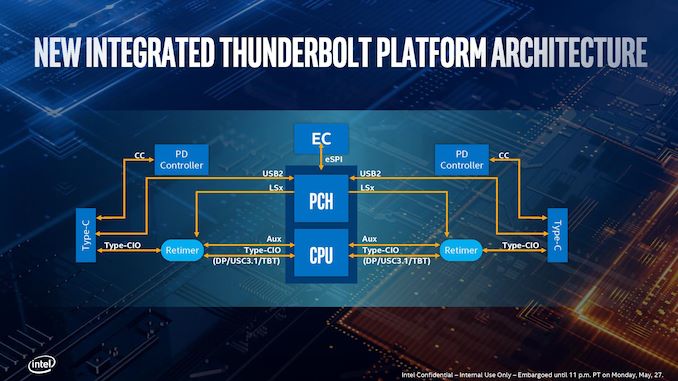

Intel has made it so each side of the CPU can support two TB3 links direct from the processor. There is still some communication back and forth with the chipset (PCH), as the Type-C ports need to have USB modes implemented. It’s worth noting that TB3 can’t be directly used out of the box, however.

Out of the four ports, it will be highly OEM dependent on how many of those will actually make it into the designs – it’s not as simple as just having the CPU in the system, but other chips (redrivers) are needed to support the USB Type-C connector. Power delivery too requires extra circuitry, which costs money. So while Intel advertises TB3 support on Ice Lake, it still needs something extra from the OEMs. Intel states that a retimer for the integrated solution is only half the size compared to the ones needed with the TB3 external chips, as well as supporting two TB3 ports per retimer, therefore halving the number of retimers needed.

Here’s a more detailed schematic, showing the complexities of adding in TB3 into a chip, with the four PCIe x4 complexes shown moving out to each of the individual PHYs at the bottom, and connected back into the main SoC interconnect fabric. The display engine also has to control what mode the TB3 ports are in, and what signals are being sent. Wake up times for TB3 in this fashion, according to Intel, are actually slightly longer compared to a controller implementation, because the SoC is so tightly integrated. This sounds somewhat counterintuitive, given that the requisite hardware blocks are now closer together, but it all comes down to power domains – in a separate chip design, each segment has a separate domain with individual power up/down states. In an integrated SoC, Intel has unified the power domains to reduce complexity and die area, which means that more careful management is required but latency ultimately increases a little bit.

The other upside to the tightly coupled integration is that Intel stated that this method of TB3 is a lot more power efficient that current external chip implementations. However they wouldn’t comment on the exact power draw of the TB3 block on the chip as it corresponds to the full TDP of the design, especially in relation to localized thermal density (Intel was initially very confused by my question on this, ultimately saying that the power per bit was lower compared to the external chip, so overall system power was lower – they seemed more interested in discussing system power over chip power). Intel did state that the difference between an idle and a fully used link was 300 mW, which suggests that if all four links are in play, we’re looking at 1.2 W. When asked, Intel stated that there are three different power delivery domains within the TB3 block depending on the logic, that the system uses integrated voltage regulation, and the TB3 region has an internal power rail that is shared with some of the internal logic of the CPU. This has implications when it comes to time-to-wake and idle power, but Intel believes it has found a good balance.

Regarding USB4 support, Intel stated that it is in the design, and they are USB4 compliant at this point, but there might be changes and/or bugs which stop it from being completely certified further down the line. Intel said that it ultimately comes down to the device side of the specification, although they have put as much in as they were able given the time constraints of the design. They hope to be certified, but it’s not a guarantee yet.

Depending on who you speak to, this isn’t Intel’s first crack at putting TB3 into CPU silicon: the chip that Intel never wants to talk about, Cannon Lake, supposedly also had an early TB3 design built inside that never worked. But Intel is confident in its Ice Lake implementation, especially with supporting four ports. I wouldn’t be surprised if this comes to desktop when Intel releases its first generation 10nm desktop processors.

*The asterisk in the title of this page is because you still need external hardware in order to enable TB3.

107 Comments

View All Comments

eastcoast_pete - Tuesday, July 30, 2019 - link

Thanks Ian! One initial observation: that slide or picture from Dell showing processor options for their 2in1 has the i7 with 4 MB of cache; my guess is Dell needs a proofreader in their marketing department (:Ian Cutress - Tuesday, July 30, 2019 - link

It's likely those cache numbers are the other way round, i.e. quad core i7 with 8MB, dual core i3 with 4MB. That would align with what we would expect.eastcoast_pete - Tuesday, July 30, 2019 - link

Agree. Looks a lot like somebody at Dell didn't check after cut-and-paste. Has Dell announced expected shipping date? As a launch partner, they're likely be among the first who ship finished product.Ian Cutress - Tuesday, July 30, 2019 - link

Not yet, as far as I know.close - Tuesday, July 30, 2019 - link

Now we know the cause of Intel's manufacturing hell. Ian's been biting their wafers... :)tipoo - Tuesday, July 30, 2019 - link

iirc Dell said NDA was lifting August 1st on the ICL XPS 13FloconDeNeige - Tuesday, July 30, 2019 - link

Page 2, the table about In-Flight Stores and Loads: The values are switched around, or else the paragraph after is wrong.Otherwise looks like a great article. Still reading :)

FloconDeNeige - Tuesday, July 30, 2019 - link

Page 3 sorryDanNeely - Tuesday, July 30, 2019 - link

I'm a bit surprised to see pen support on the Athena requirement list. Everything else seems reasonable as an evolution of mainstream designs; but pens have always been very niche something I don't see changing. Even if pen support is baked into Intels <1W LCDs; including a pen's going to drive up system costs. And if loose is just going to end up lost; if a pen holster is required that's a decent amount of internal volume in increasing thin and dense designs.notashill - Tuesday, July 30, 2019 - link

There are already tons of laptops with pen support but no included pen or internal holster.