Examining Intel's Ice Lake Processors: Taking a Bite of the Sunny Cove Microarchitecture

by Dr. Ian Cutress on July 30, 2019 9:30 AM EST- Posted in

- CPUs

- Intel

- 10nm

- Microarchitecture

- Ice Lake

- Project Athena

- Sunny Cove

- Gen11

Intel’s Ice Lake and Sunny Cove

A Welcome Update, with Questions on Execution

When launching a new mobile product using a new processor design, all the parts have to come together to make it work. This means all of the following:

- The microarchitecture design

- SoC implementation

- Manufacturing

- Co-operation with partners/OEMs

- Time to Market

- Messaging

- Marketing

- Interactions with the press and consumers

- Promotion

- Price

- Competitiveness

Any one of these segments could make or break the next wave of innovation (a key phrase Intel likes to use). With Intel’s 10nm manufacturing process, and the 10th Gen Core 'Ice Lake' design, we’re moving along each of these points in turn, and it is interesting to see what the final reflection will be several years down the line. From our perspective, we now have extensive details on the core and the SoC, and Intel is slowly moving into product phase by the end of the year. We can evaluate what we’ve seen.

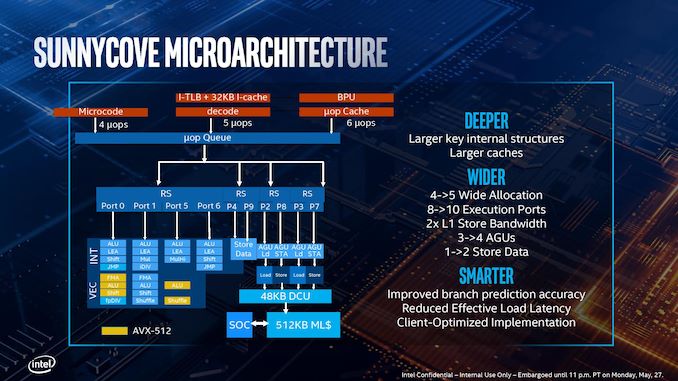

The Core and the SoC

Having ‘not another Skylake’ is a huge sigh of relief. With every new microarchitecture update, especially significant ones, we like to see how the power budget is being used and what key structures within the microarchitecture have been improved and expanded upon. The team behind the Sunny Cove core have listed some impressive hard numbers, with doubling the L1 store bandwidth, making significant L1 and L2 cache adjustments, increasing the reorder buffer a whopping +57%, and moving to a 10-port execution unit design. The inclusion of AVX-512 is welcomed by parts of the community for sure, although I expect not as many as Intel would like (this leads onto Intel’s DLBoost strategy, I’ll mention later). Assuming we can get the same +18% IPC metrics that Intel does, this is a great uplift and it will be exciting to see where we go from here.

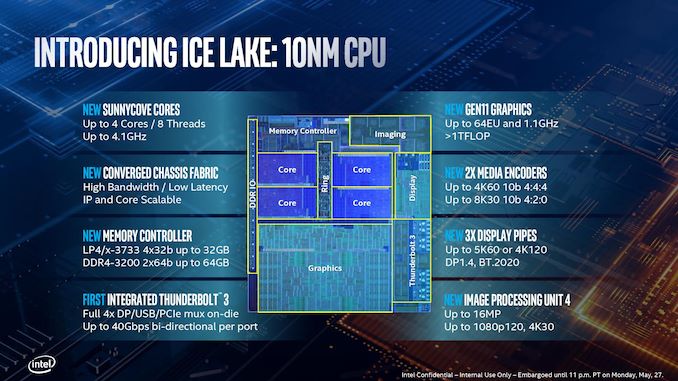

On the SoC, the big improvements to the graphics and the memory controller are my important ones here. Intel is taking integrated graphics seriously again, with an improved 64 EU design that promises to match AMD’s best at 25W. Intel has improved its memory controller significantly here, now supporting LPDDR4-3733 and DDR4-3200, which helps given that the graphics hardware is always craving memory bandwidth.

Adding Thunderbolt 3 to the SoC is going to help drive adoption in the mobile space, however speaking to a number of press, we think that because TB3 still requires an expensive controller on the device end, that the standard still has that high-cost to entry barrier, even if it ends up being cheaper for host implementation. Until non-Intel TB3 device controllers hit the market, the biggest benefit here is going to be potential support for the USB4 standard. With respect to the Wi-Fi 6 enablement, I’m not so enthused here, as it still requires an additional Intel-only proprietary CNVi module, forcing OEMs to go down an Intel route. If Intel made the CNVi standard open to all, I’d be making a bigger deal about this.

Manufacturing and Time To Market

The fact that Intel is going to end up competing against itself, with Ice Lake-U against Comet Lake-U, is akin to shooting yourself in the foot. Ultimately we expect Ice Lake-U to be focused on the premium market through Intel’s Project Athena, but Comet Lake-U is likely to span from budget to premium as well, especially if it ends up supporting more cores than Ice Lake. Ice Lake should have been a 2017 product, and Intel is only now at a point where it believes its 10nm products are viable for the market, which leads to questions on if the process is even profitable, and how many chips are going to be made available to OEMs – again, because of Project Athena, only key OEM customers going for those premium devices are going to launch initially, tailoring the messaging towards that premium feel.

Questions still surround Intel’s 10nm viability, especially given that the company has promised it is going to be producing high core count Xeons on this process node. Hopefully we can get an update on that.

Ice Lake Messaging, and Project Athena

As mentioned, the whole deal with Whiskey Lake and Comet Lake single thread CPU performance being similar to Ice Lake is going to be a mess. Part of this is down to the messaging for sure, whereby both Ice Lake and Comet Lake are going to be Intel 10th Gen, with Core i7 and Core i5/i3 variants. The only way to distinguish between the two is that Ice Lake has a G in the SKU and Comet Lake has a U, details that some of Intel’s own partners don’t disclose on product pages on websites.

One thing that Intel could lean on is the AVX-512 in Ice Lake, and its DL Boost strategy. Despite AVX-512 being inside Intel’s Xeons, the amount of ‘consumer-grade’ software that uses it is very minimal. By moving it into the consumer platforms, and enabling features like VNNI, Intel wants to drive AI-software solutions into the market. One example we were given was the ability for image software to sort images by what it detects in them – and having this all done locally (and securely) on the CPU, rather than the cloud. If Intel can execute on DL Boost for consumers, it could be a big win, and an easy benefit over the competition.

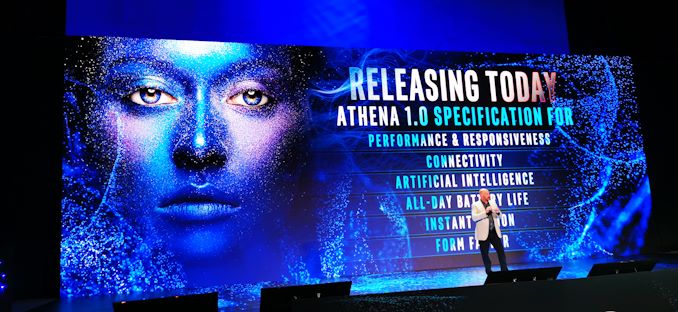

Turning to Project Athena – I’m all in favor of driving innovation forward and defining specifications that help push new and innovative form factors to enhance the user experience. But as you might have guessed, as it stands, I’m not its biggest fan. The Athena ecosystem is its own closed playground – in order for OEMs to play ball, they have to meet a number of requirements, a sizable chunk of which are only beneficial through Intel-only hardware. For example, Athena devices need Wi-Fi 6, which can be provided by an M.2 module or a CNVi RF chip. Athena devices also need substantial battery life, and the best way to achieve that is by using a CNVi RF option – but Intel is the only one that can make them because the CNVi standard is proprietary.

If an OEM doesn’t want to use Intel’s Wi-Fi 6 solution, then it makes it harder to develop an Athena certified device. It means that OEMs have to play Intel’s game in order to compete in the space. For me, that’s a high entry fee. Sure, the certified devices at the end of day are likely to be great, but if they all have Intel Wi-Fi 6, then where’s the variation? Perhaps I’m a little altruistic here: Intel is trying to create its own certification program and to play by the rules might require investing in Intel-only designed controllers. But I feel that an effort like this works best when there’s competition at every level.

Competition

On a core-to-core level, Intel's recent designs have the following configurations:

| Microarchitecture Comparison | ||||||

| Skylake | Cannon Lake | Sunny Cove* | Zen | Zen 2 | ||

| L1-D Cache |

32 KiB/core 8-way |

32 KiB/core 8-way |

48 KiB/core 12-way |

32 KiB/core 8-way |

32 KiB/core 8-way |

|

| L1-I Cache |

32 KiB/core 8-way |

32 KiB/core 8-way |

32 KiB/core 8-way |

64 KiB/core 4-way |

32 KiB/core 8-way |

|

| L2 Cache |

256 KiB/core 4-way |

256 KiB/core 4-way |

512 KiB/core 8-way |

512 KiB/core 8-way |

512 KiB/core 8-way |

|

| L3 Cache |

2 MiB/core 16-way |

2 MiB/core 16-way |

2 MiB/core 16-way |

2 MiB/core | 4 MiB/core | |

| L3 Cache Type | Inclusive | Inclusive | Inclusive | Non-Inclusive | Non-Inclusive | |

| Decode | 4 + 1 | 4 + 1 | 4 + 1 | 4 | 4 | |

| uOP Cache | 1.5k | 1.5k | 2.25k | 2k | 4k | |

| Reorder Buffer | 224 | 224 | 352 | 192 | 224 | |

| Execution Ports | 8 | 8 | 10 | 10 | 11 | |

| AGUs | 2 + 1 | 2 + 1 | 2 + 2 | 1 + 1 | 2 + 1 | |

| AVX-512 | - | 1 x FMA | 1 x FMA | - | ||

| * Sunny Cove numbers for Client. Server will have different L2/L3 cache and FMA, like Skylake | ||||||

Where AMD has reduced the size of the L1-D cache (to fit in a 4k micro-op cache), Intel has increased it. Both AMD and Intel now sit with 512 KiB L2 caches, although AMD is 4 MiB of non-inclusive cache to Intel's 2 MiB of inclusive cache. Intel has a much larger re-order buffer, and made improvements to its address generation units to help feed the cores. It's becoming ever more important to feed the beast.

Final Thought of the Day

Looking through the Ice Lake and Sunny Cove design, I have to give kudos to Intel’s engineers. The core microarchitecture looks solid, and there is no doubt that Intel will have a raw single thread performance advantage in the mobile space. I’m glad that Intel is taking its graphics solutions seriously again, and between the CPU and GPU, it’s good to see that extra power budget going to good use. I can’t wait to have the hardware on hand.

If you’re listening Intel, please consider the following: I haven’t seen any plans to bring Ice Lake to the desktop, but can we get a quad-core Ice Lake-U at 35W in a desktop processor form factor, for $179?

107 Comments

View All Comments

eastcoast_pete - Tuesday, July 30, 2019 - link

Thanks Ian! One initial observation: that slide or picture from Dell showing processor options for their 2in1 has the i7 with 4 MB of cache; my guess is Dell needs a proofreader in their marketing department (:Ian Cutress - Tuesday, July 30, 2019 - link

It's likely those cache numbers are the other way round, i.e. quad core i7 with 8MB, dual core i3 with 4MB. That would align with what we would expect.eastcoast_pete - Tuesday, July 30, 2019 - link

Agree. Looks a lot like somebody at Dell didn't check after cut-and-paste. Has Dell announced expected shipping date? As a launch partner, they're likely be among the first who ship finished product.Ian Cutress - Tuesday, July 30, 2019 - link

Not yet, as far as I know.close - Tuesday, July 30, 2019 - link

Now we know the cause of Intel's manufacturing hell. Ian's been biting their wafers... :)tipoo - Tuesday, July 30, 2019 - link

iirc Dell said NDA was lifting August 1st on the ICL XPS 13FloconDeNeige - Tuesday, July 30, 2019 - link

Page 2, the table about In-Flight Stores and Loads: The values are switched around, or else the paragraph after is wrong.Otherwise looks like a great article. Still reading :)

FloconDeNeige - Tuesday, July 30, 2019 - link

Page 3 sorryDanNeely - Tuesday, July 30, 2019 - link

I'm a bit surprised to see pen support on the Athena requirement list. Everything else seems reasonable as an evolution of mainstream designs; but pens have always been very niche something I don't see changing. Even if pen support is baked into Intels <1W LCDs; including a pen's going to drive up system costs. And if loose is just going to end up lost; if a pen holster is required that's a decent amount of internal volume in increasing thin and dense designs.notashill - Tuesday, July 30, 2019 - link

There are already tons of laptops with pen support but no included pen or internal holster.