Qualcomm's New Snapdragon S4: MSM8960 & Krait Architecture Explored

by Brian Klug & Anand Lal Shimpi on October 7, 2011 12:35 PM EST- Posted in

- Smartphones

- Snapdragon

- Arm

- Qualcomm

- Krait

- MDP

- Mobile

- SoCs

Cache & Memory Hierarchy

Qualcomm has a three level exclusive cache hierarchy in Krait. The lower two levels are private per core, while the third level is shared among all cores. Qualcomm calls these caches L0, L1 and L2.

Each Krait core has an 8KB L0 cache (4KB instruction + 4KB data cache). The L0 cache is direct mapped and accessible in a single cycle. Qualcomm claims an 85% hit rate in this level 0 cache, which helps save power by not firing up the larger L1 cache. The hierarchy is exclusive so L0 data isn't necessarily duplicated in L1.

Each core also has a 32KB L1 cache (16KB instruction + 16KB data). The L1 4-way set associative and can also be accessed in a single cycle. There's no way prediction at work here. With 1 cycle latency to both L0 and L1, the primary advantage here is power.

| Krait Cache Architecture | |||||

| Size | Architecture | Frequency | |||

| L0 | 4KB + 4KB | Direct Mapped | Core | ||

| L1 | 16KB + 16KB | 4-way set associative | Core | ||

| L2 | 1MB (dual core) or 2MB (quad core) | 8-way set associative | 1.3GHz max | ||

The L2 cache is shared among all cores. In dual-core designs the L2 cache is sized at 1MB (up from 512KB in Scorpion), while quad-core Krait SoCs will have a 2MB L2. Krait's L2 cache is 8-way set associative.

While the L0 and L1 caches operate at core frequency and are on the same voltage plane as their associated core, the L2 cache is separate. To save power the L2 cache runs at its own frequency (up to 1.3GHz depending on the currently requested performance level). The L2 cache is on its own power plane and can be power gated if necessary.

Although Scorpion featured a dual-channel LPDDR2 memory controller, in a PoP configuration only one channel was available to any stacked DRAM. In order to get access to both 32-bit memory channels the OEM had to implement a DRAM on-package as well as an external DRAM on the PCB. Memory requests could be interleaved between the two DRAM, however Qualcomm seemed to prefer load balancing between the two with CPU/GPU accesses being directed to the lower latency PoP DRAM. Very few OEMs seemed to populate both channels and thus Scorpion based designs were effectively single-channel offerings.

Krait removes this limitation and now OEMs can utilize both memory channels in a PoP configuration (simply put two 32-bit DRAM die on the PoP stack) or in an external configuration. The split PoP/external DRAM organization is no longer supported. This change will hopefully mean we'll see more dual-channel Krait designs than we saw with Scorpion, which will in turn improve performance.

Process Technology and Clock Speeds

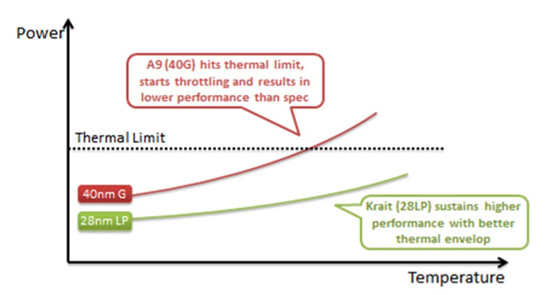

Krait will be the world's first smartphone CPU built on a 28nm process. Qualcomm is working with both TSMC and Global Foundries, although TSMC will produce the first chips. Krait will be built, at first, on TSMC's standard 28nm LP process. According to Qualcomm there's less risk associated with TSMC's non-HKMG process. Qualcomm was quick to point out that the entire MSM8960 SoC is built on a 28nm LP process compared to NVIDIA's 40nm LPG design in Kal-El. From Qualcomm's perspective, 40nm G transistors are only useful at reducing leakage at high temperatures but for the majority of the time a homogeneous LP design makes more sense.

Just like Scorpion, Krait places each core on its own voltage plane driven at its own clock frequency. Cores can be clocked independently of one another, which Qualcomm insists gives it a power advantage in many workloads.

The first implementation of Krait will be in a dual-core 1.5GHz MSM8960, however a second revision of the silicon will be introduced next year that increases clock speed to 1.7 - 2.0GHz. Qualcomm claims that at the same 1.05V core voltage, Krait can run at 1.7GHz vs. 1.55GHz for Scorpion. At these two clock speeds and at the same voltage, Qualcomm tells us that Krait consumes 265mW of power vs. 432mW running an undisclosed workload. Although it should be possible to draw more power than Scorpion under load, Krait should hopefully be able to improve overall power efficiency by completing tasks quicker and thus dropping down to idle faster than its predecessor. Smartphone and tablet battery life should remain the same at worst and improve at best, as a result.

108 Comments

View All Comments

DanNeely - Friday, October 7, 2011 - link

Static ram (the kind used in CPU caches) has always been much faster than the dynamic ram used for main system memory.SRAM uses a block of a half dozen transistors to store a bit as a stable logic state; as a result it can operate as fast as any other transistor based device in an IC. The number of clock cycles a cache bank needs to complete an access operation is primarily a factor of its size, both because it takes more work to select a specific part and because signalling delays due to the speed of electric signals through the chip become significant at gigahertz speeds. Size isn't the only speed factor in how fast a cpu cache operators; higher associativity levels can improve worst case behavior (by reducing misses due to pathalogical memory access patterns) significantly at the cost of slowing all operations slightly.

DRAM has a significantly different design, it only uses a single transistor per bit and stores the data in a paired capacitor. This allows for much higher memory capacities in a single chip and much lower costs/GB as a result. The catch is that reading the capacitors charge level and then recharging it after the check takes significantly longer. The actual memory cells in a DDR3-1600 chip are only operating at 200mhz (up from 100-133mhz a decade ago); other parts of the chips operate much faster as they access large numbers of memory cells in parallel to keep the much faster memory bus fed.

Blaster1618 - Saturday, October 8, 2011 - link

Thank you for such a clear and thorough response.MonkeyPaw - Friday, October 7, 2011 - link

Isn't it amazing how these low-power architectures are surpassing Atom in both power and performance? Atom isn't even an OoO architecture. Windows 8 and OS X Lion will be allow these architectures in netbooks and ultrabooks before we know it, and Intel's value-stripping at the low-end will finally die a terrible death.partylikeits1999 - Saturday, October 8, 2011 - link

Intel will be in very big trouble unless FinFet can get Atom's power down in the same sub 4W range as this next round of quad core chipsets from nVidia, Qualcomm and TI.Wilco1 - Saturday, October 8, 2011 - link

Even with FinFet it's impossible Atom will run at 4GHz which it needs to get comparable performance as an A15 or Krait at 2.5GHz. And in less than 2W. Atom has been dead in the water for a while now - it cannot keep up with ARM out-of-order cores on performance, power consumption or integration despite Intel's process advantage.Tomasthanes - Friday, October 7, 2011 - link

Yes, I could go to Google. It's just better journalism to define acronyms (even common ones) as you use them.Baron Fel - Friday, October 7, 2011 - link

system on a chip. At this point for Anand it would be like writing CPU as central processing unit.bjacobson - Saturday, October 8, 2011 - link

silly me been saying silicon on chip in my head all these years never stopped to think it through >.<bjacobson - Friday, October 7, 2011 - link

very exciting. Soon I won't have any need of a dedicated desktop except for gaming or a laptop except for business.Zingam - Saturday, October 8, 2011 - link

So you basically need a desktop and a laptop?