IBM Creates First 2nm Chip

by Dr. Ian Cutress on May 6, 2021 6:00 AM EST

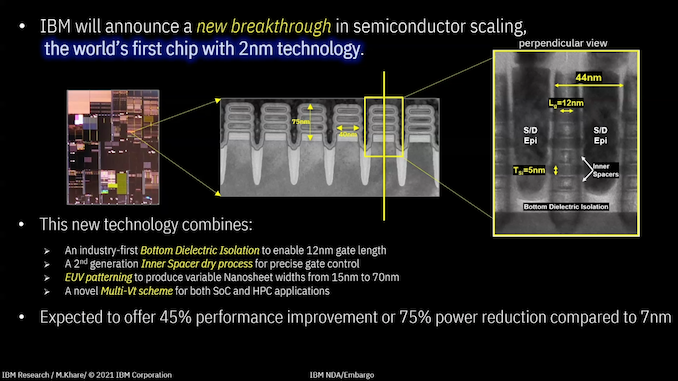

Every decade is the decade that tests the limits of Moore’s Law, and this decade is no different. With the arrival of Extreme Ultra Violet (EUV) technology, the intricacies of multipatterning techniques developed on previous technology nodes can now be applied with the finer resolution that EUV provides. That, along with other more technical improvements, can lead to a decrease in transistor size, enabling the future of semiconductors. To that end, Today IBM is announcing it has created the world’s first 2 nanometer node chip.

Names for Nodes

Just to clarify here, while the process node is being called ‘2 nanometer’, nothing about transistor dimensions resembles a traditional expectation of what 2nm might be. In the past, the dimension used to be an equivalent metric for 2D feature size on the chip, such as 90nm, 65nm, and 40nm. However with the advent of 3D transistor design with FinFETs and others, the process node name is now an interpretation of an ‘equivalent 2D transistor’ design.

Some of the features on this chip are likely to be low single digits in actual nanometers, such as transistor fin leakage protection layers, but it’s important to note the disconnect in how process nodes are currently named. Often the argument pivots to transistor density as a more accurate metric, and this is something that IBM is sharing with us.

Transistor Density

Today’s announcement states that IBM’s 2nm development will improve performance by 45% at the same power, or 75% energy at the same performance, compared to modern 7nm processors. IBM is keen to point out that it was the first research institution to demonstrate 7nm in 2015 and 5nm in 2017, the latter of which upgraded from FinFETs to nanosheet technologies that allow for a greater customization of the voltage characteristics of individual transistors.

IBM states that the technology can fit ’50 billion transistors onto a chip the size of a fingernail’. We reached out to IBM to ask for clarification on what the size of a fingernail was, given that internally we were coming up with numbers from 50 square millimeters to 250 square millimeters. IBM’s press relations stated that a fingernail in this context is 150 square millimeters. That puts IBM’s transistor density at 333 million transistors per square millimeter (MTr/mm2).

For comparison:

| Peak Quoted Transistor Densities (MTr/mm2) | ||||

| AnandTech | IBM | TSMC | Intel | Samsung |

| 22nm | 16.50 | |||

| 16nm/14nm | 28.88 | 44.67 | 33.32 | |

| 10nm | 52.51 | 100.76 | 51.82 | |

| 7nm | 91.20 | 237.18* | 95.08 | |

| 5nm | 171.30 | |||

| 3nm | 292.21* | |||

| 2nm | 333.33 | |||

| Data from Wikichip, Different Fabs may have different counting methodologies * Estimated Logic Density |

||||

As you can tell, different foundries have different official names with a variety of densities. It’s worth noting that these density numbers are often listed as peak densities, for transistor libraries where die area is the peak concern, rather than frequency scaling – often the fastest parts of a processor are half as dense as these numbers due to power and thermal concerns.

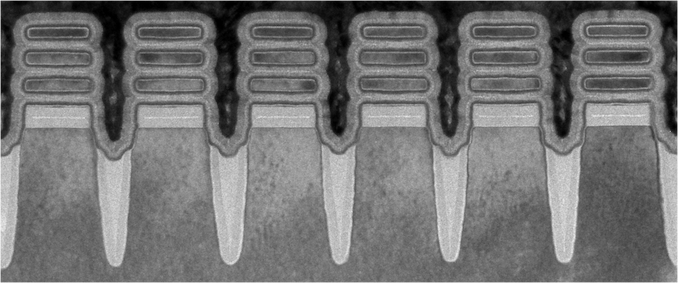

With regards the movement to Gate-All-Around / nanosheet transistors, while not explicitly stated by IBM, images show that this new 2nm processor is using a three-stack GAA design. Samsung is introducing GAA at 3nm, while TSMC is waiting until 2nm. Intel by contrast, we believe, will introduce some form of GAA on its 5nm process.

IBM’s 3-stack GAA uses a cell height of 75 nm, a cell width of 40 nm, and the individual nanosheets are 5nm in height, separated from each other by 5 nm. The gate poly pitch is 44nm, and the gate length is 12 nm. IBM says that its design is the first to use bottom dieletric isolation channels, which enables the 12 nm gate length, and that its inner spacers are a second generation dry process design that help enable nanosheet development. This is complimented by the first use of EUV patterning on the FEOL parts of the process, enabling EUV at all stages of the design for critical layers.

Users might be wondering why we’re hearing that IBM is the first to a 2nm chip. IBM is one of the world’s leading research centers on future semiconductor technology, and despite not having a foundry offering of their own, IBM develops IP in collaboration with others for their manufacturing facilities. IBM sold its manufacturing to GlobalFoundries with a 10 year partnership commitment back in 2014, and IBM also currently works with Samsung, and recently announced a partnership with Intel. No doubt the latter two will be partnering with IBM on some level around this new development for its viability in their own production chain.

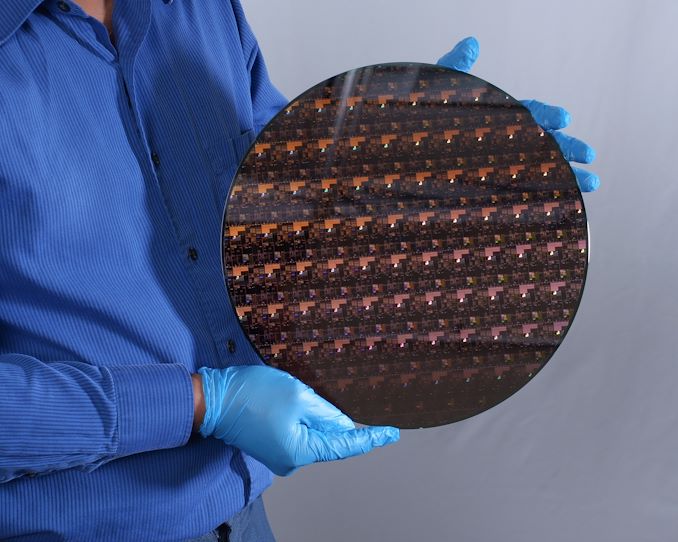

No details on the 2nm test chip have been provided, although at this stage it is likely to be a simplified SRAM test vehicle with a little logic. The 12-inch wafer images showcase a variety of different light diffractions, which likely points to a variety of test cases to affirm the viability of the technology. IBM says that the test design uses a multi-Vt scheme for high-performance and high-efficiency application demonstrations.

The chip was designed and made at IBM’s Albany research facility, which features a 100,000 sq. ft. clean room. The purpose of this facility is to build on IBM’s expansive patent and licensing portfolio for collaborations with partners.

We have a set of questions with IBM’s experts awaiting response. We also now have an active invitation to go visit, as and when we can travel again.

Related Reading

- IBM and AMD to Advance Confidential Computing

- Hot Chips 2020 Live Blog: IBM z15, a 5.2 GHz Mainframe CPU (11:00am PT)

- IBM & Partners to Fight COVID-19 with Supercomputers, Forms COVID-19 HPC Consortium

- Hot Chips 31 Live Blogs: IBM's Next Generation POWER

- IBM to use Samsung 7nm EUV for Next-Gen POWER and z CPUs

- IBM And Everspin Announce 19TB NVMe SSD With MRAM Write Cache

- TSMC Update: 2nm in Development, 3nm and 4nm on Track for 2022

- Intel’s Manufacturing Roadmap from 2019 to 2029: Back Porting, 7nm, 5nm, 3nm, 2nm, and 1.4 nm

118 Comments

View All Comments

storapa - Friday, May 7, 2021 - link

That's a trick question! My answer is: 1.44" (or maybe 3.5" assuming you meant 1440KiB capacity floppy drives).Peskarik - Thursday, May 6, 2021 - link

I have 5900X lying at home, unopened.According to all the reviews - amazing processor, fast and energy efficient.

Then one starts to read user experience - WHEA Errors, constant reboots, BSODs.

One has to tinker for hours, days, months to get a Zen3 system stable.

The AMD QC seems to be absolute garbage, push as many cpus out as possible, RMA the bad ones, and the user is the unpaid beta tester.

My i7-2600K runs flawless since 10 years, on the other hand. I never had to tweak or troubleshoot anything, and I am a complete build-and-forget novice.

Intel has failed me. I do not want AMD, I want Intel, but I do not want slow and extremely hot chip.

It is sad.

Machinus - Thursday, May 6, 2021 - link

My 5950x worked perfectly out of the box. Sell me your 5900,Peskarik - Saturday, May 8, 2021 - link

Decided to take my chances. :-)Will build up my first AMD system now.

jsz - Thursday, May 6, 2021 - link

3900x here. 100% stable in a critical work environment granted I am using ECC ram.Pretty sure a lot of these AMD "issues" involve unstable IMC's and RAM being pushed higher than it should. I know a lot of people want to run DDR4 3600 due to infinity fabric performance, but I think things like disconnect issues and what not stem from the IMC not being stable enough per sample basis.

AMD claims DDR4 3200(SR)/2993(DR) is supported, but they make no note of JEDEC or otherwise.

Intel has been much more conservative with official DDR4 specs even though they have a better memory controller, but it makes sense from this perspective.

Oxford Guy - Thursday, May 6, 2021 - link

'even though they have a better memory controller'Do they? I know that was true in the past but AMD is now on the third iteration of Zen.

jsz - Thursday, May 6, 2021 - link

Ryzen 3000/5000 cant really clock past 1900 FCLK and even this is potentially rare without overriding the voltage on some chips. Most seem to peak around 1800 FCLK, but I would expect some people to have instability. The 2700X I tested prior to my 3900x wouldn't even do 3200 with B-die ram. Went back to 7700k until 3000 series was released.. Glad I waited since the core count helps work flow.Current Rocket lake pushes further with a 1:1 memory clock setting relative to Ryzen 3000/5000 and Skylake IMC on late 10th is technically superior to both.. at least in terms of overall latency. Rocket lake is a little more stable past 4400mhz.

the_eraser1 - Thursday, May 6, 2021 - link

You conflate the IMC with overall memory system.Yes, Comet Lake has better memory latency, but that has to do with its monolithic and more integrated architecture. Same for Rocket Lake, which *does* feature a better IMC, but actually does not go further in 1:1 mode; most RKL IMCs have trouble pushing past 3200, with 3600 being quite rare. Ryzen 3000 series very commonly pushes 3600, and 5000 series reaches 1900 quite easily, with some even reaching 2000.

However, this is moot as the gear ratios between the two architectures are substantially different. The fact remains that 3000 and 5000 series can fairly easily support memory speeds in excess of 5000 MT/s; the gearing ratio is largely independent of the actual IMC and has more to do with infinity fabric limits.

Also, if you look at the monolithic designs for Ryzen, you will find that (until RKL), Renoir was the king of memory overclocking.

Of course, Intel has effectively retaken that crown with RKL, as its gearing ratio has a smaller impact on performance than AMD, and can still reach incredible speeds with excellent timings, edging out even R5000 series in that regard.

jsz - Thursday, May 6, 2021 - link

I suppose they just trade off in different areas and my mistake as I do not own and never used a RKL CPU. Just see a lot of different things going on with the chip.We can agree that SKL and the revised CML variation is sort of the king when it comes to overall latency between high clocked memory and its controller (intel ring). RKL seems to generally go higher due to offset gearing and better PCB quality (Layer count and better memory tracing on later boards)

I didn't know rocket lake struggled on 1:1 as I've seen some chips do 2000mhz memory clock but that might be one off results. I know theres a lot of hwbot records being broken with geardown which is why I assumed. Does make sense though.. 11900K was originally spec'd as the only chip that had an official 3200 1:1 spec (2933 for everything else), but I guess they updated marketing/product pages later on. Perhaps microcode updates boosted internal voltage? Not sure.

From what I understand about Ryzen, is that the I/O Die for both 3000 and 5000 is the same but global foundries should be getting better consistency with chips over time. AMD claimed the 5000 IMC can do up to 2000 FCLK 1:1 but no one seems to be able to push it over 1900, at least consistently enough for daily use.

Ryzen still has a larger latency penalty relative to Both Skylake and Rocketlake regardless of gearing which is unfortunate, but 5000 improves it by 10 or so ns due to the more monolithic 8 core die per chiplet.

And yes I agree, Sweet spot for Ryzen seems to be high clocked 3600-3800 ram in 1:1 mode due to IF, but I do think people might not realize certain instabilities of the I/O die resulting in WHEA errors assuming bad luck with the silicon lottery.

Peskarik - Thursday, May 6, 2021 - link

so you suggest running at 3200, do you?When I read overclock.net thread (75 pages) that I have linked below, where people have tried everything to get their Ryzen 5000x stable, including stock bios settings for everything (including RAM), I get a different feeling.

Some people have had their chips replaced through RMA, put them into their systems, without any changes between chip changes, and suddenly things worked fine.